从以太网PHY,MAC及其通信界面开始

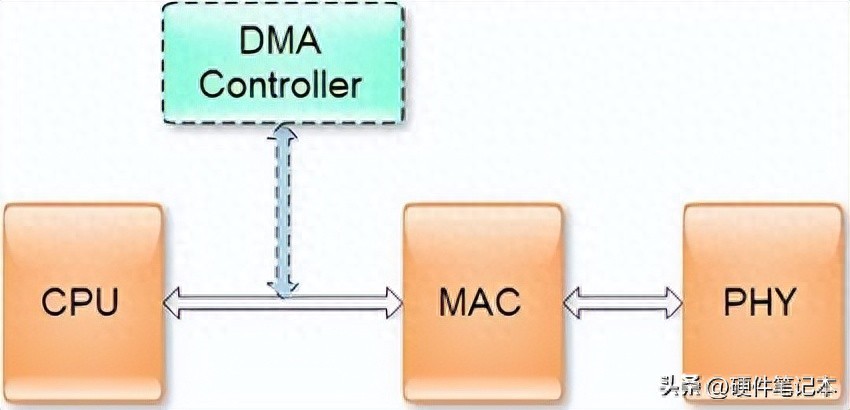

本文主要介绍以太网的Mac和Phy,以及MII(媒体独立界面)和MII -GMII,SGMII,SGMII,RMII,RMII,RGMII等各种衍生版本。本文指出:从硬件角度来看,从硬件角度来看,以太网接口电路主要由两个部分组成:Mac(Mac(Mac)访问媒体(Mac(MAC)插入媒体)。如下图所示:DMA控制器通常属于CPU部分,并用虚线放置在此处,以表明DMA控制器可以参与网络网络数据传输。但是,在实际设计中,上三部分不一定是分开的。由于PHY结合了大量的模拟硬件,因此Mac是一种常见的全数字设备。考虑到模拟/数字混合动力车的芯片区域和架构,通常是在微控制器中使用Mac,以使PHY Off-Chip离开芯片。更灵活,更强大的芯片技术可以实现Mac和Phy的单芯片整合。它可以分为以下类型:CPU结合了MAC和PHY。目前,CPU的集成Mac很少见,PHY使用独立的芯片。更常见的CPU不包括MAC和PHY,MAC和PHY使用集成的芯片。在数据链路层和OSI层七个模型的物理层上更常见的Mac和PHY工作。详细信息如下:MAC(媒体访问控制)是媒体访问控制的子层协议。本节中有两个概念:MAC可以是硬件控制器,而Mac正在与协议交谈。该协议位于OSI层7协议中数据链路层的下半部分,主要响应以控制和连接物理层的物理介质。 MAC硬件几乎如下:在发送数据时,如果发送数据,则可以预先确定MAC协议。如果发送了,将添加一些控制信息到数据,最后将数据和信息控制发送到Physical层以指定格式。接收数据时,MAC协议首先确定输入信息是否输入以及是否发生交付错误。如果没有错误,则将删除控制信息并发送到LLC层(逻辑链接控制)。该层协议是由IEEE-802.3以太网标准指定的以太网MAC。以太网数据链路层确实包括Mac(媒体访问控制)Sublayer和LLC(逻辑链接控件)Sublayer。以太网卡Mac芯片的操作只是不必实现MGA MAC Sublayer和LLC Sublayer的操作,而且还提供了一个符合规格的PCI接口,以与主机实现数据交换。 MAC从PCI总线接收IP数据包(或其他网络层协议的数据包)后,它将其划分并重新填充到最多1518 Byte和最小64英寸的框架中。该框架包括目标MAC地址,其自己的资源MAC地址和数据包prot的类型OCOL(例如,IP数据包的类型以80表示,最后有一个Dord(4byte)CRC代码。但是目标MAC地址来自何处?它涉及ARP协议(网络和铺设层之间的协议。目标IP地址是第一次发送ARP数据包,首次发送ARP数据包,Who who who who ip ip as aptrastion iSxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx的东西?本LAN的所有主机都会收到此请求。 IPX/SPX还具有相应的协议来完成这些操作IP地址和MAC地址存储在主机系统中,称为ARP表。由驱动程序和操作系统完成。以太网MAC芯片的一端连接到计算机OFComputer PCI,另一端连接到PHY芯片,它们通过MII接口连接。 Mac的结构图如下图:PHY(物理层,PHY))是IEE802.3中指定的标准模块。 STA(站管理实体,通常管理并控制Mac或CPU)通过SMI(串行管理接口)PHY的行为和状态,并且通过在PHY中阅读和写作登记簿来实现操作的具体操作和控制。 PHY的主要结构如图所示:PHY是一个物理收发器界面,它实现了OSI模型的物理层。 IEEE-802.3标准是指以太网PHY。这包括MII/GMII(介电独立接口)Sublayer,PC(物理鳕鱼)ING Sublayer),PMA(附着的物理介质)Sublayer,PMD(物理培养基相关)Sublayer和MDI Sublayer。这遵循IEEE-802.3K中使用的规格,用于10Baset(第14条)和100basetx(第24和25条)。注意:PHY寄存器是在22.2.4 IEEE802.3标准管理部分中介绍的,但所有寄存器均未涉及。一些寄存器需要在其他章节中阅读。当然,该文件还提到了在哪里查找注册。 MII(媒体独立接口)是一个独立的媒体接口。 MII接口是连接MAC和PHY的常见接口。这将由EE-802.3以太网行业标准确定。 MII界面提供Mac和PHY,PHY和STA(车站管理)之间的互连技术。该接口支持10MB/s和100MB/S数据传输速率,位数据传输宽度为4位。下图中的MII接口iSshown:MII接口主要包括F我们的部分。一个是从MAC层到PHY层的传输数据接口,第二个是从PHY层到MAC层的接收数据接口,第三个是状态指示的信号,从PHY层到MAC层,第四个是MDIO接口,它发送MAC层和Phy层信息的控制和信息。 MII包括Mac和Phy之间的数据接口和一个管理接口:TX_CLK(发送时钟):TX_CLK(发送时钟)是连续的时钟信号(即系统开始,并且信号始终存在),它是参考时钟TX_EN,TX_EN,TXD,TXD,TX_ER PHY)。 TX_CLK驱动的PHY驱动的时钟频率为数据传输速率的25%,偏差为±100ppm。例如,在100MB/s模式下,TX_CLK时钟频率为25MHz,占空比在35%至65%之间。 TXD 3:0(传输数据):TXD由RS,TX_CLK时钟和TX_CLK时钟周期内部驱动,TX_EN有效。 TXD数据由PHY收到OTHerwise TXD数据没有PHY效应。 TX_ER(编码错误错误):用TX_CLK转动TX_ER。在数据传输过程中,如果TX_ER在一个以上的时钟周期中有效,并且TX_EN目前有效,则发送到数据通道的数据无效且无用。注意:当TX_ER有效时,当PHY或TX_EN无效时,它不会影响数据传输。在MII接口连接中,如果未使用TX_ER信号线,则应将其拉入地面。 tx_en:发送启用。 TX_EN将根据TX_CLK的上升边缘同时通过BeingSublayer认罪来转换。 RX_CLK:它的要求与TX_CLK相同,只是这是RX_DV,RXD,RX_ER的参考时钟(信号方向从PHY到Rs)。 RX_CLK也由PHY驱动。 PHY可以从接收到的数据中提取rx_clk,也可以是从名义参考时钟(例如TX_CLK参考)驱动rx_clk。 RXD 3:0(接收数据):RXD由RS驱动,即-rx_clk,在RX_CLK时钟周期内,RX_DV是有效的。 RXD数据由RS接收,否则RXD数据将对Rs产生影响。 RX_ER(接收错误):RX_ER已经在RX_CLK中,其在RX通道中的作用类似于TX_ER对TX通道数据传输的效果。 RX_DV(接收数据有效):RXD_DV变成RX_CLK,并由PHY驱动。操作NIS就像频道运输中的TX_EN一样。不同之处在于,时间安排有很小的区别:为了使RS成功接收数据,RXD_DV有效的时间必须覆盖整个帧过程,也就是说,因为不得晚于框架定界符(SFD)的开始,并且排除了框架末端的任何末端。 MII将数据发送到4位nibble模式,时钟速率为25MHz。它的工作率可以达到100MB/s。 COL(注意到碰撞):COL无需能够能够能够参考时钟。 CRS(载体Sense):CRS不需要引用参考。只要渠道具有交付或接受过程,CRS就必须有效。 MDC:提供PHY Station管理的管理管理,以参考将信息发送到MDIO信号的时间。 AOF MDC是一个非周期信号,没有最大或最小时间。不管TX_CLK和RX_CLK的标称周期如何,MDC的最小高和低时间应为160 ns,MDC的最小周期为400 ns。 MDIO:是PHY和STA之间的双向信号。它用于传递PHY和STA之间的控制信息和状态。控制信息由MDC的STA驱动,并与PHY结合使用。状态信息是在MDC的同一时间驱动的,并与STA结合使用。一些PHY寄存器由IEEE定义,因此PHY反映了其当前状态。 Mac继续通过SMI总线读取PHY状态寄存器以确定当前的pHy状态。例如,连接速度,双工功能等当然,您还可以设置PHY寄存器bysmi必须实现控制的目标。例如,控件控件被打开和关闭,自我表达模式或强制模式等。无论是物理连接的MII总线和SMI总线,还是状态寄存器和PHY控制寄存器都由IEEE控制。因此,不同公司的Mac和Phys可以以协调的方式工作。当然,为了与不同公司的物理合作,需要相应地更改驾驶员。 MII支持10Mbps和100Mbps操作。一个接口由14条电线组成,其支撑非常灵活。但是,缺点是它在端口上使用了如此多的信号线。如果8端口开关需要使用112条电线,端口16中的224条电线,而端口32中的448条电线。通常,该接口不现实。因此,Themodern开关将使用MII简化的其他标准,例如RMII,SMII,GMII等。RMII端口使用两条电线发送数据,MII端口使用4条线来发送数据,而GMII使用8条线来运送数据。 MII/RMII只是一个接口。对于10Mbps线性速度,MII时钟速率为2.5MHz,而对于RMII,为5MHz;对于100Mbps的线性速度,MII所需的时钟速率为25MHz,对于RMII,为50MHz。 MII/RMII用于运输以太网数据包。 MII/RMII接口为4/2bit。在以太网中,需要将串行转换,编解码器等发送到弯曲对和光纤。它的框架格式符合IEEE 802.3(10m)/IEEE 802.3U(100m)/IEEE 802.1Q(VLAN)。以太网框架格式为:序列 +启动位 +目标MAC地址 +源MAC地址 +类型/长度 +数据 +填充(可选) + 32Bitcrc。如果有VLAN,则在类型/长度之后添加2个字节VLAN标签,其中12位用于表示VLAN ID,并使用4bit来表示数据优先级! GMII是千兆网络的MII接口,它还具有相应的RGMII接口WHICH表示简化的GMII接口。 GMII采用了8位接口数据,并具有125MHz的操作时钟,因此传输速率可以达到1000Mbps。它也与MII指定的10/100 Mbps工作模式兼容。 GMII接口数据结构符合IEEEE以太网标准,并且该接口的定义在IEEE 802.3-2000中显示。 RGMII(减少千兆介质独立接口),简化GMII接口。 Compared to GMII, RGMII has the following characteristics: Shipment/receive data lineswas modified from 8 to 4 tx_er and tx_en multiplexed, and the RX_ER and RX_DV had many TX_CTL, and the rate of 1 Gbit/s was sent by RX_CTL, and the clock frequency was 125mhz100 Mbit/s rate was transferred, and the clock was 25mhz10.在MBIT/s速率下,时钟频率为2.5MHz信号的定义如下:尽管RGMII信号线被划分,但TXC/RXC时钟仍为125MHz。为了达到1000Mbit的传输速率,TXD/RXD信号LIne sends and receives TXD [3: 0]/RXD [3: 0] at the GMII interface to the rising edge of the clock, and sends and receives the TXD [7: 4]/RXD [7: 4] on the falling edge of the clock, Tx_en and tx_er state, sends tx_en to the rising edge of TXC and sends tx_er to the falling edge.尝试将相同的原理用于RX_CTL。下图是运输和尚未尚未达到的时机:SMI:串行管理接口,通常称为MDIO接口(管理)。数据输入/输出接口)。 MDIO首先是在IEEE 802.3的22卷中定义的,最终,MDIO的增强版本是在第45卷中定义的。主要在Mac层和以太网PHY之间应用,并用于MAC层设备通过读取和写入注册器来实现PHY层设备的操作和管理。 MDIO的主机(即形成MDC时钟的设备)通常称为STA(站管理),而MDIO从Slave通常称为MMD(MDIO管理设备)。通常STA是一部分MAC层设备的位置,而MMD是PHY层设备的一部分。 MDIO接口包括两行MDIO和MDC,其中MDIO是双向数据线,themDC是由STA驱动的时钟线。最大MDC时钟速度通常为2.5MHz,并且MDC也可能无法固定,甚至不固定。 MDIO接口只是MDC时钟上升边缘的一个示例,并且不在MDC时钟频率(类似于I2C接口)。如下图所示。该网卡在最后两个OSI层中工作,即物理层和数据链路层。物理层标识了电信号和光学信号,线状态,时钟引用,数据折扣以及传递和接收数据所需的电路,并为数据链路层设备提供了通用的接口。物理层芯片称为PHY。数据链路层提供响应机制,数据框架的构建,评估数据误差,控制和阻塞液网络层上的标准数据接口。以太网卡上的数据链路层中的芯片称为MAC控制器。许多网卡的两个部分都完成了。它们之间的关系是PCI总线连接到MAC总线,MAC和PHY和网络电缆(当然,它不是直接连接的,并且还有一个变压器设备)。 Mac和Phy由IEEE指定的标准MII/GIGAMII(媒体独立互动)接口连接。该界面由IEEE定义。 MII接口提供网络中的所有数据和数据控制。 MAC确定PHY的工作状态,并使用SMI(串行管理接口)控制PHY来读取PHY寄存器。 IEEE还指定了一些PHY寄存器。通过这种方式,PHY在登记册中显示其当前状态。 Mac A继续通过SMI巴士阅读PHY状态寄存器,以找出当前的PHY状态,例如Cour的连接速度,双工能力等SE,PHY寄存器也可以通过SMI设置,以实现控制的目标,例如In和Off Flow Control,自动谈判模式或强制模式等。不同公司的Mac和Phy可以协调。当然,要匹配不同公司的PHS独特操作,需要相应地更改驾驶员。

本文主要介绍以太网的Mac和Phy,以及MII(媒体独立界面)和MII -GMII,SGMII,SGMII,RMII,RMII,RGMII等各种衍生版本。本文指出:从硬件角度来看,从硬件角度来看,以太网接口电路主要由两个部分组成:Mac(Mac(Mac)访问媒体(Mac(MAC)插入媒体)。如下图所示:DMA控制器通常属于CPU部分,并用虚线放置在此处,以表明DMA控制器可以参与网络网络数据传输。但是,在实际设计中,上三部分不一定是分开的。由于PHY结合了大量的模拟硬件,因此Mac是一种常见的全数字设备。考虑到模拟/数字混合动力车的芯片区域和架构,通常是在微控制器中使用Mac,以使PHY Off-Chip离开芯片。更灵活,更强大的芯片技术可以实现Mac和Phy的单芯片整合。它可以分为以下类型:CPU结合了MAC和PHY。目前,CPU的集成Mac很少见,PHY使用独立的芯片。更常见的CPU不包括MAC和PHY,MAC和PHY使用集成的芯片。在数据链路层和OSI层七个模型的物理层上更常见的Mac和PHY工作。详细信息如下:MAC(媒体访问控制)是媒体访问控制的子层协议。本节中有两个概念:MAC可以是硬件控制器,而Mac正在与协议交谈。该协议位于OSI层7协议中数据链路层的下半部分,主要响应以控制和连接物理层的物理介质。 MAC硬件几乎如下:在发送数据时,如果发送数据,则可以预先确定MAC协议。如果发送了,将添加一些控制信息到数据,最后将数据和信息控制发送到Physical层以指定格式。接收数据时,MAC协议首先确定输入信息是否输入以及是否发生交付错误。如果没有错误,则将删除控制信息并发送到LLC层(逻辑链接控制)。该层协议是由IEEE-802.3以太网标准指定的以太网MAC。以太网数据链路层确实包括Mac(媒体访问控制)Sublayer和LLC(逻辑链接控件)Sublayer。以太网卡Mac芯片的操作只是不必实现MGA MAC Sublayer和LLC Sublayer的操作,而且还提供了一个符合规格的PCI接口,以与主机实现数据交换。 MAC从PCI总线接收IP数据包(或其他网络层协议的数据包)后,它将其划分并重新填充到最多1518 Byte和最小64英寸的框架中。该框架包括目标MAC地址,其自己的资源MAC地址和数据包prot的类型OCOL(例如,IP数据包的类型以80表示,最后有一个Dord(4byte)CRC代码。但是目标MAC地址来自何处?它涉及ARP协议(网络和铺设层之间的协议。目标IP地址是第一次发送ARP数据包,首次发送ARP数据包,Who who who who ip ip as aptrastion iSxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx的东西?本LAN的所有主机都会收到此请求。 IPX/SPX还具有相应的协议来完成这些操作IP地址和MAC地址存储在主机系统中,称为ARP表。由驱动程序和操作系统完成。以太网MAC芯片的一端连接到计算机OFComputer PCI,另一端连接到PHY芯片,它们通过MII接口连接。 Mac的结构图如下图:PHY(物理层,PHY))是IEE802.3中指定的标准模块。 STA(站管理实体,通常管理并控制Mac或CPU)通过SMI(串行管理接口)PHY的行为和状态,并且通过在PHY中阅读和写作登记簿来实现操作的具体操作和控制。 PHY的主要结构如图所示:PHY是一个物理收发器界面,它实现了OSI模型的物理层。 IEEE-802.3标准是指以太网PHY。这包括MII/GMII(介电独立接口)Sublayer,PC(物理鳕鱼)ING Sublayer),PMA(附着的物理介质)Sublayer,PMD(物理培养基相关)Sublayer和MDI Sublayer。这遵循IEEE-802.3K中使用的规格,用于10Baset(第14条)和100basetx(第24和25条)。注意:PHY寄存器是在22.2.4 IEEE802.3标准管理部分中介绍的,但所有寄存器均未涉及。一些寄存器需要在其他章节中阅读。当然,该文件还提到了在哪里查找注册。 MII(媒体独立接口)是一个独立的媒体接口。 MII接口是连接MAC和PHY的常见接口。这将由EE-802.3以太网行业标准确定。 MII界面提供Mac和PHY,PHY和STA(车站管理)之间的互连技术。该接口支持10MB/s和100MB/S数据传输速率,位数据传输宽度为4位。下图中的MII接口iSshown:MII接口主要包括F我们的部分。一个是从MAC层到PHY层的传输数据接口,第二个是从PHY层到MAC层的接收数据接口,第三个是状态指示的信号,从PHY层到MAC层,第四个是MDIO接口,它发送MAC层和Phy层信息的控制和信息。 MII包括Mac和Phy之间的数据接口和一个管理接口:TX_CLK(发送时钟):TX_CLK(发送时钟)是连续的时钟信号(即系统开始,并且信号始终存在),它是参考时钟TX_EN,TX_EN,TXD,TXD,TX_ER PHY)。 TX_CLK驱动的PHY驱动的时钟频率为数据传输速率的25%,偏差为±100ppm。例如,在100MB/s模式下,TX_CLK时钟频率为25MHz,占空比在35%至65%之间。 TXD 3:0(传输数据):TXD由RS,TX_CLK时钟和TX_CLK时钟周期内部驱动,TX_EN有效。 TXD数据由PHY收到OTHerwise TXD数据没有PHY效应。 TX_ER(编码错误错误):用TX_CLK转动TX_ER。在数据传输过程中,如果TX_ER在一个以上的时钟周期中有效,并且TX_EN目前有效,则发送到数据通道的数据无效且无用。注意:当TX_ER有效时,当PHY或TX_EN无效时,它不会影响数据传输。在MII接口连接中,如果未使用TX_ER信号线,则应将其拉入地面。 tx_en:发送启用。 TX_EN将根据TX_CLK的上升边缘同时通过BeingSublayer认罪来转换。 RX_CLK:它的要求与TX_CLK相同,只是这是RX_DV,RXD,RX_ER的参考时钟(信号方向从PHY到Rs)。 RX_CLK也由PHY驱动。 PHY可以从接收到的数据中提取rx_clk,也可以是从名义参考时钟(例如TX_CLK参考)驱动rx_clk。 RXD 3:0(接收数据):RXD由RS驱动,即-rx_clk,在RX_CLK时钟周期内,RX_DV是有效的。 RXD数据由RS接收,否则RXD数据将对Rs产生影响。 RX_ER(接收错误):RX_ER已经在RX_CLK中,其在RX通道中的作用类似于TX_ER对TX通道数据传输的效果。 RX_DV(接收数据有效):RXD_DV变成RX_CLK,并由PHY驱动。操作NIS就像频道运输中的TX_EN一样。不同之处在于,时间安排有很小的区别:为了使RS成功接收数据,RXD_DV有效的时间必须覆盖整个帧过程,也就是说,因为不得晚于框架定界符(SFD)的开始,并且排除了框架末端的任何末端。 MII将数据发送到4位nibble模式,时钟速率为25MHz。它的工作率可以达到100MB/s。 COL(注意到碰撞):COL无需能够能够能够参考时钟。 CRS(载体Sense):CRS不需要引用参考。只要渠道具有交付或接受过程,CRS就必须有效。 MDC:提供PHY Station管理的管理管理,以参考将信息发送到MDIO信号的时间。 AOF MDC是一个非周期信号,没有最大或最小时间。不管TX_CLK和RX_CLK的标称周期如何,MDC的最小高和低时间应为160 ns,MDC的最小周期为400 ns。 MDIO:是PHY和STA之间的双向信号。它用于传递PHY和STA之间的控制信息和状态。控制信息由MDC的STA驱动,并与PHY结合使用。状态信息是在MDC的同一时间驱动的,并与STA结合使用。一些PHY寄存器由IEEE定义,因此PHY反映了其当前状态。 Mac继续通过SMI总线读取PHY状态寄存器以确定当前的pHy状态。例如,连接速度,双工功能等当然,您还可以设置PHY寄存器bysmi必须实现控制的目标。例如,控件控件被打开和关闭,自我表达模式或强制模式等。无论是物理连接的MII总线和SMI总线,还是状态寄存器和PHY控制寄存器都由IEEE控制。因此,不同公司的Mac和Phys可以以协调的方式工作。当然,为了与不同公司的物理合作,需要相应地更改驾驶员。 MII支持10Mbps和100Mbps操作。一个接口由14条电线组成,其支撑非常灵活。但是,缺点是它在端口上使用了如此多的信号线。如果8端口开关需要使用112条电线,端口16中的224条电线,而端口32中的448条电线。通常,该接口不现实。因此,Themodern开关将使用MII简化的其他标准,例如RMII,SMII,GMII等。RMII端口使用两条电线发送数据,MII端口使用4条线来发送数据,而GMII使用8条线来运送数据。 MII/RMII只是一个接口。对于10Mbps线性速度,MII时钟速率为2.5MHz,而对于RMII,为5MHz;对于100Mbps的线性速度,MII所需的时钟速率为25MHz,对于RMII,为50MHz。 MII/RMII用于运输以太网数据包。 MII/RMII接口为4/2bit。在以太网中,需要将串行转换,编解码器等发送到弯曲对和光纤。它的框架格式符合IEEE 802.3(10m)/IEEE 802.3U(100m)/IEEE 802.1Q(VLAN)。以太网框架格式为:序列 +启动位 +目标MAC地址 +源MAC地址 +类型/长度 +数据 +填充(可选) + 32Bitcrc。如果有VLAN,则在类型/长度之后添加2个字节VLAN标签,其中12位用于表示VLAN ID,并使用4bit来表示数据优先级! GMII是千兆网络的MII接口,它还具有相应的RGMII接口WHICH表示简化的GMII接口。 GMII采用了8位接口数据,并具有125MHz的操作时钟,因此传输速率可以达到1000Mbps。它也与MII指定的10/100 Mbps工作模式兼容。 GMII接口数据结构符合IEEEE以太网标准,并且该接口的定义在IEEE 802.3-2000中显示。 RGMII(减少千兆介质独立接口),简化GMII接口。 Compared to GMII, RGMII has the following characteristics: Shipment/receive data lineswas modified from 8 to 4 tx_er and tx_en multiplexed, and the RX_ER and RX_DV had many TX_CTL, and the rate of 1 Gbit/s was sent by RX_CTL, and the clock frequency was 125mhz100 Mbit/s rate was transferred, and the clock was 25mhz10.在MBIT/s速率下,时钟频率为2.5MHz信号的定义如下:尽管RGMII信号线被划分,但TXC/RXC时钟仍为125MHz。为了达到1000Mbit的传输速率,TXD/RXD信号LIne sends and receives TXD [3: 0]/RXD [3: 0] at the GMII interface to the rising edge of the clock, and sends and receives the TXD [7: 4]/RXD [7: 4] on the falling edge of the clock, Tx_en and tx_er state, sends tx_en to the rising edge of TXC and sends tx_er to the falling edge.尝试将相同的原理用于RX_CTL。下图是运输和尚未尚未达到的时机:SMI:串行管理接口,通常称为MDIO接口(管理)。数据输入/输出接口)。 MDIO首先是在IEEE 802.3的22卷中定义的,最终,MDIO的增强版本是在第45卷中定义的。主要在Mac层和以太网PHY之间应用,并用于MAC层设备通过读取和写入注册器来实现PHY层设备的操作和管理。 MDIO的主机(即形成MDC时钟的设备)通常称为STA(站管理),而MDIO从Slave通常称为MMD(MDIO管理设备)。通常STA是一部分MAC层设备的位置,而MMD是PHY层设备的一部分。 MDIO接口包括两行MDIO和MDC,其中MDIO是双向数据线,themDC是由STA驱动的时钟线。最大MDC时钟速度通常为2.5MHz,并且MDC也可能无法固定,甚至不固定。 MDIO接口只是MDC时钟上升边缘的一个示例,并且不在MDC时钟频率(类似于I2C接口)。如下图所示。该网卡在最后两个OSI层中工作,即物理层和数据链路层。物理层标识了电信号和光学信号,线状态,时钟引用,数据折扣以及传递和接收数据所需的电路,并为数据链路层设备提供了通用的接口。物理层芯片称为PHY。数据链路层提供响应机制,数据框架的构建,评估数据误差,控制和阻塞液网络层上的标准数据接口。以太网卡上的数据链路层中的芯片称为MAC控制器。许多网卡的两个部分都完成了。它们之间的关系是PCI总线连接到MAC总线,MAC和PHY和网络电缆(当然,它不是直接连接的,并且还有一个变压器设备)。 Mac和Phy由IEEE指定的标准MII/GIGAMII(媒体独立互动)接口连接。该界面由IEEE定义。 MII接口提供网络中的所有数据和数据控制。 MAC确定PHY的工作状态,并使用SMI(串行管理接口)控制PHY来读取PHY寄存器。 IEEE还指定了一些PHY寄存器。通过这种方式,PHY在登记册中显示其当前状态。 Mac A继续通过SMI巴士阅读PHY状态寄存器,以找出当前的PHY状态,例如Cour的连接速度,双工能力等SE,PHY寄存器也可以通过SMI设置,以实现控制的目标,例如In和Off Flow Control,自动谈判模式或强制模式等。不同公司的Mac和Phy可以协调。当然,要匹配不同公司的PHS独特操作,需要相应地更改驾驶员。